- 您现在的位置:买卖IC网 > Sheet目录2000 > IDTCV146PVG (IDT, Integrated Device Technology Inc)IC FLEXPC CLK PROGR P4 56-SSOP

COMMERCIALTEMPERATURERANGE

4

IDTCV146

PROGRAMMABLEFLEXPCCLOCKFORP4PROCESSOR

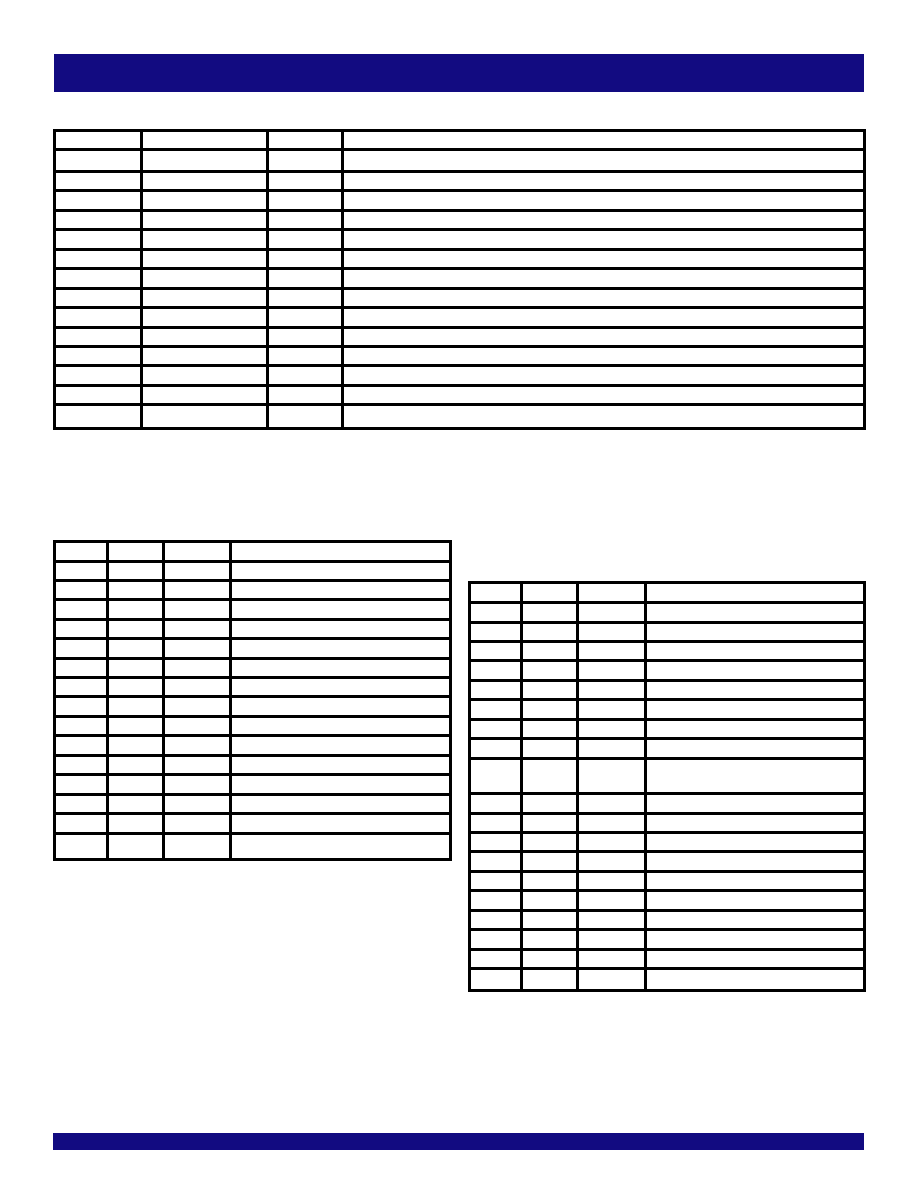

PIN DESCRIPTION (CONT.)

Pin Number

Name

Type

Description

43

CPUC1

OUT

Host 0.7V current mode differential clock output

44

CPUT1

OUT

Host 0.7V current mode differential clock output

45

VDD_CPU

PWR

3.3V

46

CPUC0

OUT

Host 0.7V current mode differential clock output

47

CPUT0

OUT

Host 0.7V current mode differential clock output

48

VSS_CPU

GND

49

SCL

I N

SM bus clock

50

SDA

I/O

SM bus data

51

XTAL_OUT

OUT

Xtaloutput

52

XTAL_IN

I N

Xtalinput

53

VSS_REF

GND

54

REF1/ FSA

I/O

14.318 MHz reference clock output. CPU frequency selection at VTT_PWRGD# assertion.

55

REF0/ FSC

I/O

14.318 MHz reference clock output. CPU frequency selection at VTT_PWRGD# assertion.

56

VDD_REF

PWR

3.3V

INDEX BLOCK WRITE PROTOCOL

Bit

# of bits

From

Description

1

Master

Start

2-9

8

Master

D2h

10

1

Slave

Ack (Acknowledge)

11-18

8

Master

Register offset byte (starting byte)

19

1

Slave

Ack (Acknowledge)

20-27

8

Master

Byte count, N (0 is not valid)

28

1

Slave

Ack (Acknowledge)

29-36

8

Master

first data byte (Offset data byte)

37

1

Slave

Ack (Acknowledge)

38-45

8

Master

2nd data byte

46

1

Slave

Ack (Acknowledge)

:

Master

Nth data byte

Slave

Acknowledge

Master

Stop

INDEX BLOCK READ PROTOCOL

Master can stop reading any time by issuing the stop bit without waiting

until Nth byte (byte count bit30-37).

Bit

# of bits

From

Description

1

Master

Start

2-9

8

Master

D2h

10

1

Slave

Ack (Acknowledge)

11-18

8

Master

Register offset byte (starting byte)

19

1

Slave

Ack (Acknowledge)

20

1

Master

RepeatedStart

21-28

8

Master

D3h

29

1

Slave

Ack (Acknowledge)

30-37

8

Slave

Byte count, N (block read back of N

bytes), power on is 8

38

1

Master

Ack (Acknowledge)

39-46

8

Slave

first data byte (Offset data byte)

47

1

Master

Ack (Acknowledge)

48-55

8

Slave

2nd data byte

Ack (Acknowledge)

:

Master

Ack (Acknowledge)

Slave

Nth data byte

Not acknowledge

Master

Stop

INDEX BYTE WRITE

Setting bit[11:18] = starting address, bit[20:27] = 01h.

INDEX BYTE READ

Setting bit[11:18] = starting address. After reading back the first data byte,

master issues Stop bit.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDTCV149PAG

IC FLEXPC CLK PROGR K8 56-TSSOP

IDTNW6005ASG

IC CALLER ID DECODER 20SOIC

IDTNW6006AS

IC CALLER ID DECODER 20-SOIC

IDTSSTE32882HLBBKG

IC REGISTERING CLK DRIVER 176BGA

IDTSSTE32882KA1AKG

IC REGISTERING CLK DRIVER 176BGA

ISD1750SYR

IC VOICE REC/PLAY 50SEC 28-SOIC

ISD5008EYI

IC VOICE REC/PLAY 4-8MIN 28-TSOP

ISL12008IB8Z

IC RTC I2C LO-POWER 8-SOIC

相关代理商/技术参数

IDTCV146PVG8

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV149PA

功能描述:IC FLEXPC CLK PROGR K8 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV149PA8

功能描述:IC FLEXPC CLK PROGR K8 56-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV149PAG

功能描述:IC FLEXPC CLK PROGR K8 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV149PAG8

功能描述:IC FLEXPC CLK PROGR K8 56-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件

IDTCV152

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:PROGRAMMABLE FLEXPC CLOCK FOR P4 PROCESSOR

IDTCV152PVG

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDTCV152PVG8

功能描述:IC FLEXPC CLK PROGR P4 56-SSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:FlexPC™ 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT